# **NY7 Series**

# Single-Chip 4-bit MCU with 8~24 I/O, 8-ch Speech/MIDI Synthesizer

# Version 1.5

May 7, 2018

NYQUEST TECHNOLOGY CO. reserves the right to change this document without prior notice. Information provided by NYQUEST is believed to be accurate and reliable. However, NYQUEST makes no warranty for any errors which may appear in this document. Contact NYQUEST to obtain the latest version of device specifications before placing your orders. No responsibility is assumed by NYQUEST for any infringement of patent or other rights of third parties which may result from its use. In addition, NYQUEST products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of NYQUEST.

# **Revision History**

| Version | Date       | Description                                                                                                                                                                                                                                                                                                                                                                           | Modified Page                 |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 1.0     | 2013/06/28 | Formal release.                                                                                                                                                                                                                                                                                                                                                                       |                               |

| 1.1     | 2013/08/16 | <ol> <li>Add 4 mask options for Push-Pull analog volume adjustment.</li> <li>Revise the description of <i>Chapter 2.10.1 Speech Synthesis</i>.</li> <li>Provide the example code of ramp-up/ramp-down for DAC output.</li> <li>Flag Z will not be affected by instruction MVLA.</li> <li>Instruction LDPR, RBDPR, RDN and RDNI belong to category of "Other Instructions".</li> </ol> | 7, 25<br>23<br>51<br>56<br>57 |

| 1.2     | 2014/01/02 | Modify Data Transfer Instruction.                                                                                                                                                                                                                                                                                                                                                     | 16, 63                        |

| 1.3     | 2014/08/27 | <ol> <li>Modify the default value of weak input pull-high resistor.</li> <li>Modify RRC and RLC command.</li> </ol>                                                                                                                                                                                                                                                                   | 10, 21<br>66                  |

| 1.4     | 2015/07/30 | Modify Instruction "RET" is 2-word.                                                                                                                                                                                                                                                                                                                                                   | 58, 81                        |

| 1.5     | 2018/05/07 | Add Instruction "MPG".                                                                                                                                                                                                                                                                                                                                                                | 58, 59, 83                    |

# Table of Contents

| Chapter 1. Introduction                                     | 6  |

|-------------------------------------------------------------|----|

| 1.1 General Description                                     | 6  |

| 1.2 Features                                                | 6  |

| 1.3 Product List                                            | 8  |

| 1.4 Block Diagram                                           | 9  |

| 1.5 Pad Description                                         |    |

| 1.6 Electrical Characteristics                              |    |

| 1.6.1 Absolute Maximum Rating                               | -  |

| 1.6.2 DC Characteristics                                    |    |

|                                                             |    |

| Chapter 2. Hardware Architecture                            |    |

| 2.1 Overview                                                | 11 |

| 2.1.1 Function Block Diagram                                |    |

| 2.1.2 Hardware Summary Table                                |    |

| 2.2 Clock Generator                                         |    |

| 2.3 System Reset                                            | 12 |

| 2.3.1 Power-On Reset (POR)                                  | 12 |

| 2.3.2 Low Voltage Reset (LVR)                               |    |

| 2.3.3 Watch-Dog Timer Reset (WDTR)                          |    |

| 2.3.4 I/O Port External Reset                               |    |

| 2.4 Address Pointer                                         | 13 |

| 2.4.1 Program Counter (PC)                                  |    |

| 2.4.2 Stack (STK)                                           |    |

| 2.4.3 Multi-function Register Pointer (RPT)                 |    |

| 2.4.4 Head Voice Pointer (HVPR) & Tail Voice Pointer (TVPR) |    |

| 2.4.5 Data Pointer (DPR)                                    |    |

| 2.5 Arithmetic Logic Unit (ALU)                             |    |

| 2.5.1 ALU Instruction Summary                               |    |

| 2.5.2 ALU Related Status Flag                               |    |

| 2.6 Memory Organization                                     |    |

| 2.6.1 ROM                                                   |    |

| 2.6.2 RAM                                                   |    |

| 2.7 I/O Ports                                               | 19 |

| 2.7.1 Pull-High Input Mode                                  |    |

| 2.7.2 Floating Input Mode                                   |    |

| 2.7.3 Output Mode                                           |    |

| 2.7.4 I/O Pin Mask Option                                   |    |

| 2.8 Infrared Transmitter                                    | 22 |

# Nyquest

| 2.9 Interrupt Generator                      | 22 |

|----------------------------------------------|----|

| 2.10 Audio Synthesizer Structure             | 23 |

| 2.10.1 Speech Synthesis                      |    |

| 2.10.2 MIDI Synthesis                        |    |

| 2.10.3 PH Value                              | 24 |

| 2.10.4 Audio Output                          |    |

| 2.10.5 Envelope Control                      |    |

| 2.10.6 Volume Control                        | 26 |

| Chapter 3. System Control                    | 27 |

| 3.1 Introduction of System Function Register | 27 |

| 3.2 RPT                                      | 29 |

| 3.3 ROD                                      |    |

| 3.4 BANK                                     |    |

| 3.5 XMD                                      |    |

| 3.6 I/O Ports Register                       |    |

| 3.7 INT                                      |    |

| 3.8 Audio Control Register                   |    |

| -                                            |    |

| 3.8.1 CHARC                                  |    |

| 3.8.2 VOL<br>3.8.3 ONOFF                     |    |

| 3.8.4 AUD                                    |    |

| 3.8.5 CHNO                                   |    |

| 3.8.6 ENVL & ENVH                            |    |

| 3.8.7 DECMD                                  |    |

| 3.9 Register Without Address Mapping         |    |

| 3.9.1 PAGE                                   |    |

| 3.9.2 Head Play Flag                         |    |

| 3.9.3 Play Flag                              |    |

| 3.9.4 PH Value Setting                       |    |

| 3.9.5 Mixer Data                             |    |

| 3.10 Audio Playback                          |    |

| 3.10.1 Voice Playback                        |    |

| 3.10.2 Melody Playback, Head-Only Mode       |    |

| 3.10.3 Melody Playback, Tail-Only Mode       |    |

| 3.10.4 Melody Playback, Head+Tail Mode       |    |

| 3.10.5 Ramp-up/Ramp-down Procedure for DAC   |    |

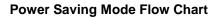

| 3.11 Power Saving Mode                       |    |

| 3.11.1 Slow Mode                             | 55 |

| 3.11.2 Halt Mode                             | 55 |

# Nyquest

| Chapter 4. Instruction Set       |    |

|----------------------------------|----|

| 4.1 Instruction Classified Table | 57 |

| 4.2 Instruction Descriptions     | 60 |

| 4.2.1 Arithmetic Instructions    |    |

| 4.2.2 Conditional Instructions   |    |

| 4.2.3 Audio Instructions         |    |

| 4.2.4 Other Instructions         |    |

# **Chapter 1. Introduction**

# **1.1 General Description**

The NY7 series IC is a powerful 4-bit micro-controller based sound processor. There are 8 channels that are configured as speech or MIDI, and all of these 8 channels or part of them can be played with speech or MIDI simultaneously. By using the high fidelity 6-bit ADPCM speech/ MIDI timbre synthesis algorithm with up to 44.1KHz sample rate, NY7 can produce near-CD quality voices. As NY7 is specially designated for MIDI synthesis application, it provides Attack-Decay-Sustain-Release method (ADSR) with 256-level envelope for Patch (instrument) synthesis. NY7 can precisely synthesize any tone frequency of MIDI with +/- 0.5% accurate internal oscillation and automatic Tone-Calibration. Therefore NY7 melody quality is very close to real instrument.

Moreover, NY7 is equipped with new Nyquest's developed high-quality noise filtering algorithm of 128KHz over-sampling, which can remove noise in order to improve speech and melody quality greatly. Up to 16-level digital volume can be applied to final synthetic speech or melody that is tailored for applications of volume adjustment. NY7A provides two kinds of audio outputs with fine resolution, one is 13-bit current-type D/A converter (DAC) and the other is 12-bit Pulse-Width-Modulation (PWM). NY7B/NY7C provide two kinds of audio outputs with fine resolution, one is 13-bit current is 13-bit current-type D/A converter (DAC) and the other is 13-bit current-type D/A converter (DAC). Therefore NY7 speech/melody quality is the best choice among all solutions.

The RISC MCU architecture is very easy to program and control, various applications can be easily implemented. There are 74 instructions, and most of them are executed in single cycle. Besides normal operation mode, NY7 also provides Halt mode (or Sleep mode) and Slow mode to minimize power dissipation.

# 1.2 Features

- Wide operating voltage range: 2.0V to 5.5V.

- 4-bit RISC type micro-controller with 74 instructions.

- NY7A have 9 items. 192K x 12-bit ROM is the maximum size.

- NY7B have 10 items. 256K x 12-bit ROM is the maximum size.

- NY7C have 19 items. 1536K x 12-bit ROM is the maximum size.

- 448x4-bit RAM, divided into 2 pages.

- Up to 4MHz system clock for instruction execution.

- Slow mode to operate with low power consumption (+/-3% accuracy).

- Halt mode to save power, less than 1uA@3V standby current.

# Nyquest

- Built-in RC oscillation is accurate with +/- 0.5% frequency deviation.

- Low voltage reset (LVR=1.9V) and watch-dog reset (WDT) are supported to protect the system.

- One interrupt entrance for multiple interrupt sources with an independent stack.

- Up to 24 flexible Bi-direction I/Os. Direction of each I/O is independently controlled by individual register bit.

- Each Bi-direction I/O pin can be optioned as different input and output function. For the input option, users can select one of three kinds of option: input with pull-high resistor, input without pull-high resistor, or input with register-controlled pull-high resistor (high-to-low wakeup only). For the output option, users can select one of three kinds of option: output with normal drive current and normal sink current, large sink current or constant sink current.

- Shared pins to provide IR carrier and external reset feature:

| Shared Pin Function    | NY7AxxxA  | NY7BxxxA  | NY7CxxxA  |

|------------------------|-----------|-----------|-----------|

| IR carrier (IR)        | PB2/IR    | PD2/IR    | PF2/IR    |

| External reset (Reset) | PB3/Reset | PD3/Reset | PF3/Reset |

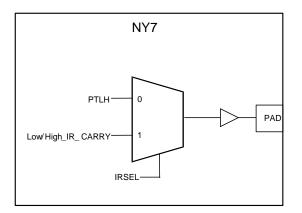

- Selection of IR carrier frequency and data high/low IR output is supported.

- Maximum of 8 channels can be played simultaneously, each channel can be arbitrarily assigned as speech or MIDI channel.

- New high fidelity 6-bit ADPCM speech synthesis algorithm and ADSR with 256-step envelope for MIDI synthesis.

- Patented noise filtering algorithm with 128KHz over sampling to enhance signal-to-noise ratio and provide excellent sound quality without ROM size increase.

- 16-level digital volume control for synthetic speech/melody.

- Built-in hardware automatic Tone-Calibration of near-zero frequency deviation for precise tone frequency.

- High quality 13-bit D/A converter, 12-bit PWM driver or 13-bit Push-Pull amplifier audio output with 4-level mask-option analog volume of 100%, 83%, 66% and 50%. (*Push-Pull output power Pout=1.3W@Vdd=5V*, THD+N=10%, F=1kHz, RL=4Ω.)

- PWM driver can be normal PWM or Ultra PWM.

# **1.3 Product List**

| P/N      | Voice Duration<br>@6KHz (sec)ROM Size<br>(bit)Program ROM<br>Size (bit)I/O |            | I/O      | PWM | DAC    | Push-<br>Pull |        |

|----------|----------------------------------------------------------------------------|------------|----------|-----|--------|---------------|--------|

| NY7A004A | 4.5                                                                        | 16K x 12   | 16K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A007A | 7.2                                                                        | 24K x 12   | 24K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A010A | 9.9                                                                        | 32K x 12   | 32K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A016A | 15.4                                                                       | 48K x 12   | 48K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A021A | 20.8                                                                       | 64K x 12   | 64K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A032A | 31.8                                                                       | 96K x 12   | 64K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A043A | 42.7                                                                       | 128K x 12  | 64K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A054A | 53.6                                                                       | 160K x 12  | 64K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7A065A | 64.5                                                                       | 192K x 12  | 64K x 12 | 8   | 12-bit | 13-bit        | -      |

| NY7B007A | 7.2                                                                        | 24K x 12   | 24K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B010A | 9.9                                                                        | 32K x 12   | 32K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B016A | 15.4                                                                       | 48K x 12   | 48K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B021A | 20.8                                                                       | 64K x 12   | 64K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B032A | 31.8                                                                       | 96K x 12   | 64K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B043A | 42.7                                                                       | 128K x 12  | 64K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B054A | 53.6                                                                       | 160K x 12  | 64K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B065A | 64.5                                                                       | 192K x 12  | 64K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B076A | 75.5                                                                       | 224K x 12  | 64K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7B087A | 86.4                                                                       | 256K x 12  | 64K x 12 | 16  | -      | 13-bit        | 13-bit |

| NY7C010A | 9.9                                                                        | 32K x 12   | 32K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C016A | 15.4                                                                       | 48K x 12   | 48K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C021A | 20.8                                                                       | 64K x 12   | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C032A | 31.8                                                                       | 96K x 12   | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C043A | 42.7                                                                       | 128K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C054A | 53.6                                                                       | 160K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C065A | 64.5                                                                       | 192K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C076A | 75.5                                                                       | 224K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C087A | 86.4                                                                       | 256K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C110A | 111.0                                                                      | 328K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C130A | 130.1                                                                      | 384K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C150A | 151.9                                                                      | 448K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C170A | 173.8                                                                      | 512K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C220A | 222.9                                                                      | 656K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C260A | 261.1                                                                      | 768K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C305A | 304.8                                                                      | 896K x 12  | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C345A | 348.5                                                                      | 1024K x 12 | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C450A | 457.8                                                                      | 1344K x 12 | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

| NY7C520A | 523.3                                                                      | 1536K x 12 | 64K x 12 | 24  | -      | 13-bit        | 13-bit |

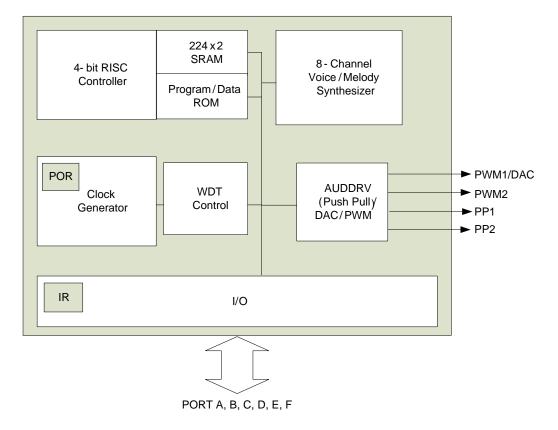

# 1.4 Block Diagram

# **1.5 Pad Description**

| Pin      | ATTR. | Description               |  |

|----------|-------|---------------------------|--|

| VDD#     | Power | Positive power            |  |

| GND#     | Power | Negative power            |  |

| PWM1/DAC | 0     | PWM1 output or DAC output |  |

| PWM2     | 0     | PWM2 output               |  |

| PP1      | 0     | Push-Pull output          |  |

| PP2      | 0     | Push-Pull output          |  |

| PA0~3    | I/O   | Bit 0~3 for Port A        |  |

| PB0~3    | I/O   | Bit 0~3 for Port B        |  |

| PC0~3    | I/O   | Bit 0~3 for Port C        |  |

| PD0~3    | I/O   | Bit 0~3 for Port D        |  |

| PE0~3    | I/O   | Bit 0~3 for Port E        |  |

| PF0~3    | I/O   | Bit 0~3 for Port F        |  |

\* NY7A: PA0~PB3, there is no Push-Pull output (PP1 & PP2).

\* NY7B: PA0~PD3, there is no PWM output (PWM1 & PWM2).

\* NY7C: PA0~PF3, there is no PWM output (PWM1 & PWM2).

# **1.6 Electrical Characteristics**

The following table lists the electrical characteristics of the NY7 EV chip. All the product's properties must refer to each part's datasheet.

### 1.6.1 Absolute Maximum Rating

| Symbol              | Parameter             | Rated Value        | Unit |

|---------------------|-----------------------|--------------------|------|

| $V_{DD}$ - $V_{SS}$ | Supply voltage        | -0.5 ~ +6.0        | V    |

| V <sub>IN</sub>     | Input voltage         | Vss-0.3V ~ Vdd+0.3 | V    |

| T <sub>OP</sub>     | Operating Temperature | 0 ~ +70            | °C   |

| T <sub>ST</sub>     | Storage Temperature   | -25 ~ +85          | °C   |

# **1.6.2 DC Characteristics**

| Symbol          | Para                    | imeter         | VDD         | Min.           | Тур.       | Max. | Unit               | Condition                                  |  |  |

|-----------------|-------------------------|----------------|-------------|----------------|------------|------|--------------------|--------------------------------------------|--|--|

| V <sub>DD</sub> | Operatir                | ng voltage     |             | 2.0            | 3.0        | 5.5  | V                  | 4MHz.                                      |  |  |

| I <sub>SB</sub> |                         | Halt mode      | 3.0         |                |            | 1    | uA                 | Sleep, no load.                            |  |  |

|                 | Supply                  |                | 4.5         |                | 000        | 1    |                    |                                            |  |  |

| I <sub>SL</sub> | Supply<br>current       | Slow mode      | 3.0<br>4.5  |                | 300<br>600 |      | uA                 | Slow, no load.                             |  |  |

|                 | Current                 |                | 3.0         |                | 5          |      |                    |                                            |  |  |

| I <sub>OP</sub> |                         | Normal mode    | 4.5         |                | 8          |      | mA                 | 4MHz, no load.                             |  |  |

|                 |                         | Weak           | 3.0         |                | 2.5        |      |                    |                                            |  |  |

|                 | Input current           | (1.2M ohms)    | 4.5         |                | 7.4        |      | uA                 |                                            |  |  |

| IIL             | (Internal<br>pull-high) | Strong         | 3.0         |                | 30         |      | uA                 | V <sub>IL</sub> =0V                        |  |  |

|                 | pui ngn)                | (100k ohms)    | 4.5         |                | 75         |      | uA                 |                                            |  |  |

| I <sub>OH</sub> | Output b                | igh current    | 3.0         |                | -7         |      | mA                 | V <sub>OH</sub> =2.0V                      |  |  |

| ЧОН             | Output II               | ightent        | 4.5         |                | -11        |      |                    | V <sub>OH</sub> =3.5V                      |  |  |

|                 |                         | ow current     | 3.0         |                | 11         |      | mA                 |                                            |  |  |

|                 | (Norma                  | Il current)    | 4.5         |                | 17         |      |                    |                                            |  |  |

| I <sub>OL</sub> |                         | ow current     | 3.0         |                | 22         |      | mA V <sub>OL</sub> | V <sub>OL</sub> =1.0V                      |  |  |

| IOL             | (Large                  | current)       | 4.5         |                | 33         |      |                    | VOL-1.0V                                   |  |  |

|                 |                         | ow current     | 3.0         |                | 20         |      | mA                 |                                            |  |  |

|                 | (Consta                 | nt current)    | 4.5         |                | 21         |      |                    |                                            |  |  |

| IDAC            | DAC out                 | put current    | 3.0         |                | 1.4        |      | mA                 | Half-scale                                 |  |  |

|                 |                         | put current    | 3.0         |                | 60         |      | mA                 |                                            |  |  |

|                 | (Norm                   | al PWM)        | 4.5         |                | 100        |      |                    |                                            |  |  |

| PWM             | PWM out                 | put current    | 3.0         |                | 80         |      | ~ ^                |                                            |  |  |

|                 | (Ultra                  | PWM)           | 4.5         |                | 125        |      | mA                 | Load=8 ohms                                |  |  |

|                 | Duck Dull a             | Duch Dull a    | Duch Dull c | autout ourroat | 3.0        |      | 180                |                                            |  |  |

| I <sub>PP</sub> | Push-Pull C             | output current | 4.5         |                | 270        |      | mA                 |                                            |  |  |

| . = /=          | Frequency deviation     |                | 3.0         |                | 0.5        |      |                    | Fosc(3.0v)-Fosc(2.4v)<br>Fosc(3v)          |  |  |

| ∆F/F            |                         | age drop       | 4.5         |                | -0.5       |      | %                  | $\frac{Fosc(4.5v)-Fosc(3.0v)}{Fosc(4.5v)}$ |  |  |

| ∆F/F            | Frequency               | lot deviation  | 3.0         | -0.5           |            | 0.5  | %                  | <u>Fmax(3.0v)-Fmin(3.0v)</u><br>Fmax(3.0v) |  |  |

| Fosc            | Oscillation             | n Frequency    |             | 3.6            | 4          | 4.1  | MHz                | VDD=2.0~5.5V                               |  |  |

Ver. 1.5 2018/05/07

# **Chapter 2. Hardware Architecture**

# 2.1 Overview

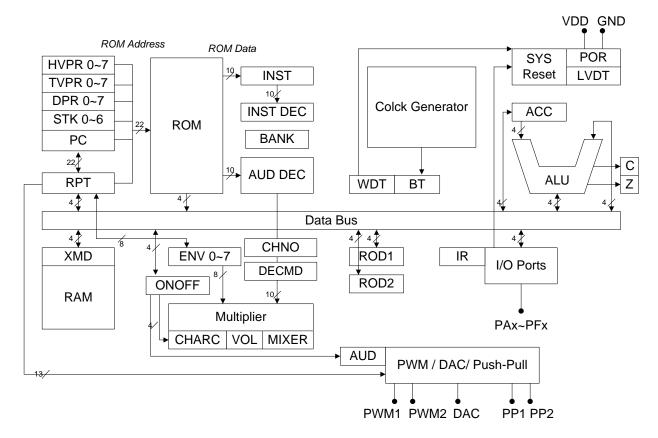

## 2.1.1 Function Block Diagram

### 2.1.2 Hardware Summary Table

| Name    | Function                                   | Address      |

|---------|--------------------------------------------|--------------|

| STK0~6  | 7-level interrupt dedicated stack          |              |

| PC      | Program counter                            |              |

| HVPR0~7 | Voice Head pointer according to SFR(CHNO). |              |

| TVPR0~7 | Voice Tail pointer according to SFR(CHNO). |              |

| DPR0~7  | Data pointer                               |              |

| RPT     | Multi-function register pointer            | SFR[0x0~0x5] |

| ENV0~7  | 8-bit Envelope of SFR (CHNO)               | SFR[0x6~7]   |

| ROD1    | ROM[7:4] data access register              | SFR[0x8]     |

| ROD2    | ROM[11:8] data access register             | SFR[0x9]     |

| CHARC   | Mix Channel#, Output choice                | SFR[0xA]     |

| AUD     | Audio output Data                          | SFR[0xB]     |

| INT     | Interrupt generator                        | SFR[0xC]     |

| DECMD   | PCM / ADPCM control register               | SFR[0xD]     |

| ONOFF   | Interrupt and audio control register       | SFR[0xE]     |

| VOL     | Digital volume control register            | SFR[0xF]     |

| Name                                            | Function                            | Address        |

|-------------------------------------------------|-------------------------------------|----------------|

| BANK                                            | Program Bank Register               | SFR[0x10]      |

| XMD                                             | Indexed RAM data access register    | SFR[0x11]      |

| CHNO                                            | Active channel select               | SFR[0x12]      |

| RAM                                             | 448 nibbles RAM                     |                |

| ROM                                             | Program & data ROM                  |                |

| Multiplier                                      | Hardware multiplier for MIDI        |                |

| Mixer                                           | Channels audio data mixer           |                |

| PWM / DAC / PP                                  | PWM, D/A or PP audio output         |                |

| INST                                            | Instruction register                |                |

| INST DEC                                        | Instruction decoder                 |                |

| AUD DEC                                         | AUD DEC Audio decoder               |                |

| Clock Generator Ring oscillator clock generator |                                     |                |

| WDT                                             | Watch-dog timer and reset generator |                |

| BT                                              | System base timer                   |                |

| SYS Reset                                       | System reset generator              |                |

| POR                                             | Power reset generator               |                |

| ACC                                             | 4-bit accumulator                   |                |

| ALU                                             | 4-bit arithmetic logic unit         |                |

| С                                               | Carry flag for arithmetic           |                |

| Z                                               | Zero flag for arithmetic            |                |

| IR                                              | Infrared transmit block             |                |

| I/O Ports                                       | I/O port register                   | SFR[0x14~0x1F] |

\*SFR[]: System Function Register

# 2.2 Clock Generator

The clock generator is a Ring oscillator, and users can only select the internal resistor oscillation (INT-R). The INT-R oscillator accuracy is up to  $\pm 0.5\%$ .

# 2.3 System Reset

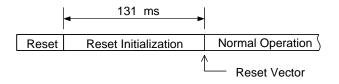

#### **Reset Initialization Procedure**

### 2.3.1 Power-On Reset (POR)

After Power-on, the power-on reset initialization will automatically be set out. After the system leaves the reset initialization procedure, it enters the normal operation and the program counter starts at the reset vector.

#### 2.3.2 Low Voltage Reset (LVR)

When the system enters the normal operation, the power supply voltage must be kept in an effective working voltage range. When the power supply voltage is lower than the effective working voltage range, the system can't work properly. To prevent the system crash, we have a low voltage detector in the NY7 IC. When the detector detects a harmful low voltage supply, it will cause a low voltage reset. The so-called "low voltage" point of the NY7 IC is approximate 1.9V.

#### 2.3.3 Watch-Dog Timer Reset (WDTR)

To recover from program function, the NY7 IC supports an embedded watch-dog timer reset. The WDTR function always works with the program executing. Users have clear the WDT periodically to prevent from timing up with a reset generation. Typically, the minimum time-up period of the WDT is about 28ms and users can clear WDT through instruction CWDT.

#### 2.3.4 I/O Port External Reset

The PB3/Reset (NY7A), PD3/Reset (NY7B) or PF3/Reset (NY7C) I/O pin of the NY7 can be optioned as a reset pin. A reset pin should always be pulled-high in normal operation, whether users use the built-in internal pull-high resister option or use an external pull-high resister on PCB with internal pull-high resister option disable. When the reset pin falls to the ground level, it generates an external reset.

#### **2.4 Address Pointer**

The NY7 micro-controller contains a program counter (PC), 8 data pointers, 7 interrupt dedicated stack (STK), a multi-function register pointer (RPT) and 8 head pointers (HVPR0~7) and 8 tail pointers (TVPR0~7) for channel 0~7. The length of each address pointer is 21-bit maximum, depends on the product parts. Users have to keep in mind that the initial value of all the pointers is unknown, except the PC.

#### 2.4.1 Program Counter (PC)

As a program instruction is executed, the PC will contain the address of the next program instruction to be executed. PC is 18-bit wide for NY7A/NY7B and 21-bit wide for NY7C. The PC starts from the reset vector (address 0x000400) after the system reset, and its value is increased by one every instruction cycle unless changed by an interrupt or a branch instructions which are listed in table below. The interrupt vector is at address 0x000000.

| Inst./Event | Function                          |

|-------------|-----------------------------------|

| JNC Addr    | Jump to {BANK, Addr} if Carry = 0 |

| JC Addr     | Jump to {BANK, Addr} if Carry = 1 |

| JNZ Addr    | Jump to {BANK, Addr} if Zero = 0  |

| JZ Addr     | Jump to {BANK, Addr} if Zero = 1  |

| Inst./Event | Function                                                                   |

|-------------|----------------------------------------------------------------------------|

| JB b, Addr  | Jump to {BANK, Addr} if A[b] = 1                                           |

| JMP Addr    | Jump to {BANK, Addr}.                                                      |

| CALL Addr   | Push the PC+2 to the STK and load {BANK, Addr} to PC.                      |

| RJMP        | Load RPT to PC, so users can execute a long jump.                          |

| RCALL       | Push the PC+2 to the STK and load RPT to PC.                               |

| Interrupt   | Push PC+2 to STK automatically.                                            |

| RET         | Pop STK back to PC. Return to the main program from subroutine             |

| IRET        | Pop STK back to PC. Return to the main program from the interrupt routine. |

Addr: 16-bit immediate address.

A[b] : b-th bit of Accumulator,  $0 \leq b \leq 3$ .

### 2.4.2 Stack (STK)

Seven level hardware push/pop stacks dedicated to the interrupt (CALL / RCALL) is available. When an interrupt takes apart, the system pushes the PC+2 (next instruction) to the STK automatically. STK occupy SFR from 0x8 to 0xE and STK is used from 0xE. When the program returns to the main program from subroutine / the interrupt routine by RET / IRET instruction, the system pops the STK back to the PC. Unused STK can be used as DPR. The STK max width is 18 bits for NY7A and 21 bits for NY7B/NY7C.

### 2.4.3 Multi-function Register Pointer (RPT)

As implied in the name, RPT are multi-function registers. There are at must six RPT that are RPT0, RPT1, RPT2, RPT3, RPT4 and RPT5. RPT0~RPT4 are 4-bit wide and RPT5 is 2-bit wide, i.e. RPT5[1:0]. The RPT max width are 18 bits for NY7A and 21 bits for NY7B/7C. Users have to operate RPT in coordination with instructions below.

| Inst./Event | Function                                            |

|-------------|-----------------------------------------------------|

| RJUMP       | Load RPT to PC, so users can execute a long jump.   |

| RCALL       | Push the PC+2 to the STK and load RPT to PC.        |

| PLAY        | Play RPT to HVPR, according to SFR(CHNO).           |

| LDSEC       | Load RPT to TVPR, according to SFR(CHNO).           |

| LDPR        | Load RPT to DPR/STK, according to SFR(CHNO).        |

| LDPH        | Load RPT[13:0] to PH, according to SFR(CHNO).       |

| RBVPR       | Read HVPR/TVPR to RPT, according to SFR(CHNO).      |

| RBDPR       | Read DPR/STK to RPT, according to SFR(CHNO).        |

| RBDA        | Read DAC data to RPT[12:0]                          |

| LDDA        | Load RPT[12:0] to DAC reg.                          |

| XMD         | Use RPT[7:0] as address to access indexed RAM data. |

#### 2.4.4 Head Voice Pointer (HVPR) & Tail Voice Pointer (TVPR)

Because NY7 is an 8-channel sound processor, 8 voice pointers each with 21-bit width are necessary for playing speech or MIDI of each channel. When PLAY is executed, the system loads RPT to HVPR of the channel that assigned by the CHNO register. When LDSEC is executed, the system loads RPT to TVPR of the channel that assigned by the CHNO register. When PLAYI is executed, the system loads immediately address to HVPR of the channel that assigned by the CHNO register. When PLAYI is executed, the system loads immediately address to TVPR of the channel that assigned by the CHNO register. When LDSECI is executed, the system loads immediately address to TVPR of the channel that assigned by the CHNO register. So users have to move the start address of the speech or MIDI data to RPT first. Besides, users can read HVPR/TVPR back by RBVPR instruction, because RBVPR moves HVPR/TVPR of the channel that assigned by the CHNO register to RPT. The HVPR/TVPR max width is 18 bits for NY7A and 21 bits for NY7B/NY7C.

#### 2.4.5 Data Pointer (DPR)

8 data pointers each with 21-bit width are necessary for reading ROM data of each channel. When LDPR is executed, the system loads RPT to DPR of the channel that assigned by the CHNO register. When LDPRI is executed, the system loads immediately address to DPR of the channel. The read back ROM data is placed on ROD2, ROD1, ACC. ACC is the 4 LSB of ROM data. Besides, users can read DPR back by RBDPR instruction, because RBDPR moves DPR of the channel that assigned by the CHNO register to RPT. The DPR max width is 18 bits for NY7A and 21 bits for NY7B/NY7C. Unused STK can be used as DPR.

# 2.5 Arithmetic Logic Unit (ALU)

The NY7 series provides a 4-bit arithmetic logic unit with a 4-bit accumulator to perform logic, unsigned arithmetic, data transfer and conditional branch operation. We have two status bits (carry and zero) to indicate the result of the operation. One or two operands will be the data sources of the ALU operation. The operands can be ACC, RAM, SFR register, or literal constant data.

### 2.5.1 ALU Instruction Summary

#### 2.5.1.1 Logic Instruction

| Instruction | Function                        | Flag Influenced |

|-------------|---------------------------------|-----------------|

| XORA m1     | $A \leftarrow M[m1]  \oplus  A$ | Z               |

| ANDA m1     | A ← M[m1] & A                   | Z               |

| ORA m1      | $A \leftarrow M[m1] \mid A$     | Z               |

| RRM m1      | Right Rotate M[m1] with C       | C, Z            |

| RLM m1      | Left Rotate M[m1] with C        | C, Z            |

| XORL L      | $A \leftarrow L  \oplus  A$     | Z               |

| ANDL L      | $A \leftarrow L \& A$           | Z               |

| Instruction | Function                | Flag Influenced |

|-------------|-------------------------|-----------------|

| ORL L       | $A \leftarrow L \mid A$ | Z               |

| RRC         | Right Rotate A with C   | C, Z            |

| RLC         | Left Rotate A with C    | C, Z            |

| RRA         | Right Rotate A          |                 |

| RLA         | Left Rotate A           |                 |

M[m1]: 4-bit RAM or SFR data at memory address m1,  $0x00 \le m1 \le 0xFF$ .

### 2.5.1.2 Arithmetic Instruction

| Instruction | Function                      | Flag Influenced |

|-------------|-------------------------------|-----------------|

| INCM m1     | M[m1] ← M[m1] + 1             | C, Z            |

| DECM m1     | M[m1] ← M[m1] - 1             | C, Z            |

| ADDA m1     | $\{C,A\} \gets A + M[m1] + C$ | C, Z            |

| ADDL L      | $A \leftarrow A + L + C$      | C, Z            |

| SUBA m      | $\{C,A\} = A - M - (\sim B)$  | C, Z            |

| SUBL L      | $\{C,A\} = A - L - (\sim B)$  | C, Z            |

| INCA        | A ← A + 1                     | C, Z            |

| DECA        | A ← A - 1                     | C, Z            |

| CPLA        | A ← 0 - A                     |                 |

M[m1]: 4-bit RAM or SFR data at memory address m1,  $0x00 \le m1 \le 0xFF$ .

B: 1-bit borrow flag data, shared with carry flag, B=~C.

#### 2.5.1.3 Data Transfer Instruction

| Instruction | Function                | Flag Influenced |

|-------------|-------------------------|-----------------|

| MVAM m1     | M[m1] ← A               |                 |

| MVMA m1     | $A \leftarrow M[m1]$    | Z               |

| MVRM m2, r  | M[m2] ← R[r]            |                 |

| MVMR m2, r  | $R[r] \leftarrow M[m2]$ |                 |

| MVLR L, r   | R[r] ← L                |                 |

| MVLA L      | $A \leftarrow L$        |                 |

| BCLR m2, b  | Clear M[m2][b]          |                 |

| BSET m2, b  | Set M[m2][b]            |                 |

| SETC        | C ← 1                   | С               |

| CLRC        | $C \leftarrow 0$        | С               |

M[m1]: 4-bit RAM or SFR data at memory address m1,  $0x00 \le m1 \le 0xFF$ .

M[m2]: 4-bit RAM at memory address m2,  $0x00 \le m2 \le 0x1F$ , means address  $0x20^{\circ}0x3F$ .

R[r]: 4-bit SFR data at register address r,  $0x0 \le r \le 0x7$ .

The width of the SFR address `r' of MVRM, MVMR, and MVLR command is 3-bit, and the MSB of the memory register is forced to be 0. So users can only use the three commands to handle RPT0~5 and

ENVL/ENVH. The width of the RAM or memory register address `m' of MVRM, and MVMR command is 5-bit, and the MSB 3-bit of the address is forced to be 0x1. Users can only use the two instructions (MVRM, MVMR) to handle RAM or memory register of address 0x20~0x3F, but the RAM page is still working.

#### 2.5.1.4 Conditional Branch Instruction

Nyquest 🚺

| Instruction | Function                                         | Flag Influenced |

|-------------|--------------------------------------------------|-----------------|

| JNC Addr    | Jump to {BANK, Addr} if Carry = 0                |                 |

| JC Addr     | Jump to {BANK, Addr} if Carry = 1                |                 |

| JNZ Addr    | Jump to {BANK, Addr} if Zero = 0                 |                 |

| JZ Addr     | Jump to {BANK, Addr} if Zero = 1                 |                 |

| JB b, Addr  | Jump to {BANK, Addr} if A[b] = 1                 |                 |

| SAGT L      | Skip when A > L                                  |                 |

| SALT L      | Skip when A < L                                  |                 |

| SANE L      | Skip when A != L                                 |                 |

| SBZ b       | Skip when A[b] = 0                               |                 |

| SBNZ b      | Skip when A[b] = 1                               |                 |

| SNHP        | Skip when head Play = 0, according to SFR(CHNO). |                 |

| SHP         | Skip when head Play = 1, according to SFR(CHNO). |                 |

| SNP         | Skip when Play = 0, according to SFR(CHNO).      |                 |

| SP          | Skip when Play = 1, according to SFR(CHNO).      |                 |

| SANP        | Skip when ALL 8 channels Play = 0                |                 |

A conditional branch instruction compares two operands and skips next instruction if expression is true. The skip operation is making an instruction NOP, not jump across it.

- $\oplus$  : Exclusive OR bitwise logical operation

- &: AND bitwise logical operation

- |: OR bitwise logical operation

- A: 4-bit Accumulator data

- C: 1-bit carry flag data

- Z: 1-bit zero flag data

- L: 4-bit immediately literal data

- M[m1]: 4-bit RAM or SFR data at memory address m1,  $0x00 \le m1 \le 0xFF$ .

- M[m2]: 4-bit RAM at memory address m2,  $0x00 \le m2 \le 0x1F$ , means address  $0x20^{\sim}0x3F$ .

- R[r]: 4-bit SFR data at register address r,  $0x0 \le r \le 0x7$ .

- A[b]: b-th bit of Accumulator,  $0 \leq b \leq 3$ .

#### 2.5.2 ALU Related Status Flag

| Symbol  | Flag  | Description                                              |

|---------|-------|----------------------------------------------------------|

| С       | Corru | C=1 if a carry-out occurs after an addition operation.   |

| C Carry |       | C=0 if a borrow-in occurs after a subtraction operation. |

| Z       | Zero  | Z=1 if the result of an ALU operation is zero.           |

Besides CLRC and SETC commands directly assign the value of the carry flag, C is influenced by the arithmetic result. C means carry and also means the complement of borrow. If the addition operation result is larger than 0xF, C=1, and C=0 if the result is  $\leq 15$ . If the subtraction operation smaller than 0, C=0, and C=1 if the result  $\geq 0$ .

### 2.6 Memory Organization

There are maximum 1.5M words ROM, 448 nibbles of RAM and 32 nibbles of dedicated System Function Register (SFR).

#### 2.6.1 ROM

A large program/data/voice single ROM is provided, and its structure is shown below. The reserved region contains system information and can't be utilized by users. After reset process is completed, NY7 will start program execution from address 0x400.

Because program page size is 64K words defined by 16-bit length address of ROM, allowable range of unconditional branch instructions JMP and CALL are limited by program page size. However, combining with 4-bit BANK register (address \$10 of System Function Register), the total program size is 1M words. If users want to branch to program which is located beyond current program bank, user can change the BANK register first and then execute JMP or CALL instruction.

If destination address is beyond 1M words, instructions RJMP and RCALL associated with RPT[20:0] can be used and BANK register is ignored. Instruction LDPRI can handle 20-bit length address of ROM.

| Address  | ROM                           |

|----------|-------------------------------|

| 0x000000 |                               |

| 0x00000F | Interrupt Vector              |

| 0x000010 |                               |

|          | Reserved                      |

| 0x0003FF |                               |

| 0x000400 |                               |

|          | Program & Data<br>Page 0      |

| 0x00FFFF |                               |

| 0x010000 |                               |

|          | Program & Data<br>Page 1 ~ 23 |

| 0x17FFFF |                               |

#### 2.6.2 RAM

There are two pages of RAM, each page of RAM contains 224 nibbles. It's total 448 nibbles. The page of RAM defined by instruction (PAGE0, PAGE1), and its initial is PAGE0. System Function Registers will occupy address space from 0x00 to 0x1F. Moreover, this address space of PAGE0 and PAGE1 are

mapped to the same System Function Registers. As consequence, the address space of PAGE0 and PAGE1 RAM which can be used by programmer is 0x20~0xFF.

The address space from 0x20 to 0x3F of PAGE0 and PAGE1 can be used with four special instructions MVRM, MVMR, BSET and BCLR. These instructions can access this range of memory space in single instruction cycle.

In addition to the immediate addressing mode, the indexed addressing mode is also supported. The page and address of the indexed RAM should be stored into RPT1 and RPT0 first, and users can read from or write in the XMD memory register to realize the indexed RAM access.

| Address | RAM                         |

|---------|-----------------------------|

| 0x00    | Quatern Euroption           |

|         | System Function<br>Register |

| 0x1F    |                             |

| 0x20    | 224 Nibbles<br>General SRAM |

| 0xFF    |                             |

(Page 0 & Page 1)

# 2.7 I/O Ports

There are at most 24 I/O pins, designated as PAx through PFx, and x=0~3. All the I/O pins are bi-directional. An individual and independent register bit can determine the direction of each I/O pin. These register bits are PAIO (SFR \$15), PBIO (SFR \$17), PCIO (SFR \$19), PDIO (SFR \$1B), PEIO (SFR \$1D) and PFIO (SFR \$1F).

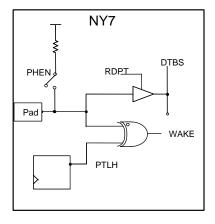

Using as input pin of each I/O, there are 3 kinds of mask option. Users can select input with pull-high resistor, input without pull-high resistor, or input with register-controlled pull-high resistor (high-to-low wakeup only). If users want to enable/disable pull-high resistor by register during program execution, only high-to-low level change on this pin can wakeup NY7. On the other hand, if the pull-high resistor is fixed by option, either high-to-low or low-to-high level change on this pin can wakeup NY7. Users can refer *Chapter 3.6 I/O Ports Register* for details.

The pull-high resister of all the I/O pins has two kinds of option: weak and strong. The weak one is about  $1.2M\Omega@3V$  for normal application and the strong one is about  $100K\Omega@3V$  usually for key matrix function. When users decide this option, the same strength of pull-high resister will be applied to every I/O pin.

Using as output pin of each I/O, there are 3 kinds of mask option. Users can select output with normal drive current and normal sink current, normal drive current and large sink current, or normal drive current and constant sink current.

Some I/O port can also be optioned as an external reset pin or an infrared (IR) output pin. A reset pin can possess a pull-high resister or not according to the mask option, which is used to enable/disable the pull-high resistor of I/O pin.

IR carrier frequency can be determined by a 5-bit option. IR carrier polarity can be initial low or high according to data value. Moreover, the IR output can provide large sink current or not according to the mask option, which is used to determine output sink current describe above.

# 2.7.1 Pull-High Input Mode

Pull-high Input Mode Configuration

Data of PA~PF, which are used as input mode, can be read in by MVMA. If the pads are not connected, a pull-high resistor will help to pull the pad toward supply voltage. All input or I/O pins can be used to wake-up the IC. In input mode, the system will be waked-up by comparing PTLH with pad voltage level. Therefore, users have to store the current pad status into PTLH before entering Halt or Slow mode. The system will be waked-up when pad voltage change is detected.

## 2.7.2 Floating Input Mode

It is similar to the pull-high input mode except the internal pull-high resistor is not connected. User should apply external pull-high resistor or pull-low resistor for high-resistance switch applications.

# 2.7.3 Output Mode

### **Output Mode Configuration**

User can select output mode to supply both normal drive current and normal/large/constant sink current by setting related mask options. But drive current of NY7 is always weaker than normal sink current, about half the scale.

# 2.7.4 I/O Pin Mask Option

Nyquest 🕪

This Section will describe the summary of available functionalities for each I/O pin. All functionalities are determined by setting of corresponding mask options.

| Category | I/O pin                      | Option                                                        | Default Value                  |

|----------|------------------------------|---------------------------------------------------------------|--------------------------------|

|          |                              | Normal I/O.                                                   | Enable                         |

|          | PAx<br>PB0 ~ PB1             | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

|          |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          |                              | IR carrier output or Normal I/O.                              | User Selection                 |

| NY7A     | PB2/IR                       | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

| NT/A     |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          |                              | Reset input or Normal I/O.                                    | User Selection                 |

|          | PB3/Reset                    | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

|          |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          | Ali I/O                      | Weak or strong input pull-high resistor.                      | Weak ( <mark>1.2MΩ</mark> @3V) |

|          | PAx                          | Normal I/O.                                                   | Enable                         |

|          | PBx<br>PCx                   | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

|          | PD0 ~ PD1                    | Normal, large or constant sink current output.                | Normal sink                    |

|          |                              | IR carrier output or Normal I/O.                              | User Selection                 |

|          | PD2/IR                       | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

| NY7B     |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          | PD3/Reset                    | Reset input or Normal I/O.                                    | User Selection                 |

|          |                              | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

|          |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          | All I/O                      | Weak or strong input pull-high resistor.                      | Weak ( <mark>1.2MΩ</mark> @3V) |

|          | PAx, PBx                     | Normal I/O.                                                   | Enable                         |

|          | PCx, PDx<br>PEx<br>PF1 ~ PF2 | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

|          |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          |                              | IR carrier output or Normal I/O.                              | User Selection                 |

|          | PF2/IR                       | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

| NY7C     |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          |                              | Reset input or Normal I/O.                                    | User Selection                 |

|          | PF3/Reset                    | Input with pull-high, floating or register-control pull-high. | Pull-high                      |

|          |                              | Normal, large or constant sink current output.                | Normal sink                    |

|          | Ali I/O                      | Weak or strong input pull-high resistor.                      | Weak (1.2MΩ@3V)                |

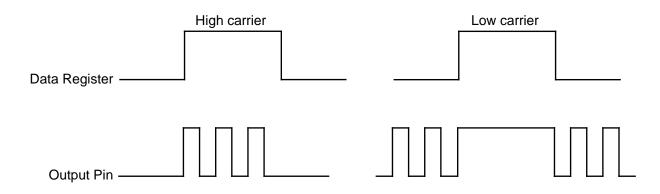

# 2.8 Infrared Transmitter

The NY7 series provides an infrared transmitter block, which is used to send infrared signal. Users can use PB2, PD2 or PF2 as an IR output. Users can option to determine the IR carrier frequency and IR Low/High carrier. The IR Low/High carrier means that if users option the IR Low carrier, the IR output pin sends infrared signal when the I/O port register value is low, and vice versa.

The IR frequency is programmable by 5 bits mask option, which can make frequency of IR carrier between 31.25KHz and 58.82KHz.

| Category | Option              | Description      |

|----------|---------------------|------------------|

| IR       | IR frequency        | 31.25 ~ 58.82KHz |

|          | IR low/high carrier | Low              |

|          |                     | High             |

# 2.9 Interrupt Generator

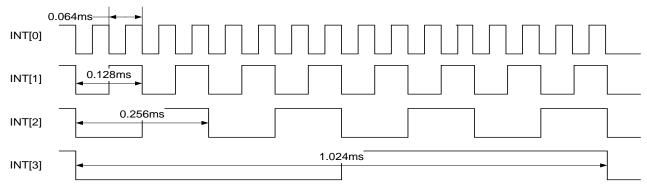

There is one hardware interrupt in NY7. The interrupt event is a fixed interval, which is derived from system base timer (BT). There is a system base timer in the NY7 IC, which functions as long as the IC isn't in the halt mode. NY7 provides 4 kinds of fixed intervals from the system base timer for interrupt source: 0.064ms, 0.128ms, 0.256ms and 1.024ms. In Slow mode, there are 4 kinds of base timer interval for polling: 1.024ms, 2.048ms, 4.096ms and 16.384ms. When using interrupts, user must select interrupt source first and then turn on. However, the time interval from BT is enabled to first occurrence of interrupt may be not as accurate as specified due to NY7 characteristic.

As an interrupt occurs, NY7 stores the accumulator (ACC), carry flag (C), zero flag (Z) and RAM page (PG) automatically. PG is controlled by the command (PAGE0, PAGE1). Then NY7 move PC+2 to STK, and jump to the interrupt vector (0x000000). An interrupt routine finishes with an IRET instruction. The IC draws back ACC, C, Z and PG back, and moves STK to PC back to jump back the main program. The interrupt event of BT will be automatically cleared after entering the interrupt routine.

# Nyquest

# 2.10 Audio Synthesizer Structure

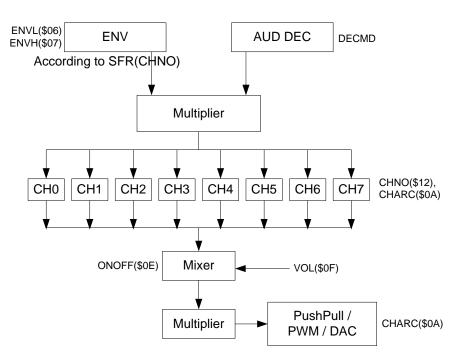

NY7 provides a built-in speech/MIDI synthesizer. The synthesizer consists of eight channels for voice or MIDI synthesis. The allowable simultaneous synthesis channel can be 2, 4, 6 and 8. The block diagram of the synthesizer unit is shown in figure below.

### 2.10.1 Speech Synthesis

NY7 supports 10-bit PCM and encoded 6-bit ADPCM speech data. The PCM voice has higher quality, but it occupies double ROM space than the ADPCM one. By cooperating with embedded noise filter of 128KHz over-sampling, it could decode high fidelity voice data even if you adapt ADPCM voice. It means you could store longer voice duration or provide more kinds of patch at lower sampling rate but enrich user's applications without degradation of sound quality.

# 2.10.2 MIDI Synthesis

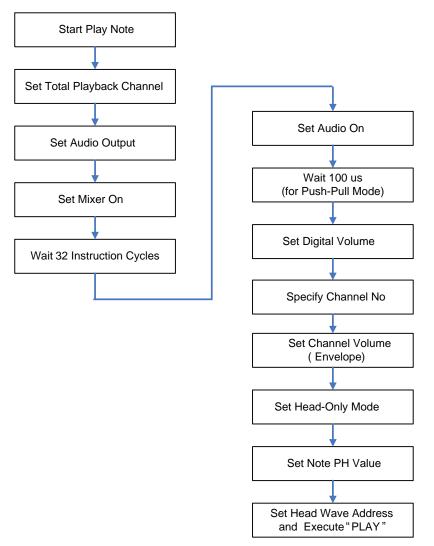

There are three combinations to form a patch in NY7. The first way (called Head-Only) is to record a complete waveform, then play it by playing whole wave only. This is the best way to represent a high quality patch, but the price has to pay is the ROM cost. In contrast, user can extract the periodic part of a patch (called Tail-Only), then play it by playing the periodic wave repeatedly. The ROM occupied by this kind of patch is minimal, however, sound quality is sacrificed.

The compromise architecture is "Head+Tail" with envelope information, which is called ADSR. During MIDI synthesis, the Head wave is played only once and the Tail wave is always repeated to generate the synthesis output. Generally, the Head wave is used to represent the non-regular part at the beginning of a patch or to represent a whole of general voice or sound effect. The Tail wave is to

represent a periodic cycle in the regular and periodic part in a patch. The Head wave and Tail wave are usually extracted from the same waveform and Tail wave is immediately successive to Head wave. This patch synthesis method can dramatically reduce ROM size needed to store the patch data.

Besides, a hardware circuit of automatic Tone-Calibration is built-in. It can result in near-zero frequency deviation for precise generation of tone frequency.

# Note: There is a limitation about Tail waves that sample number of Tail waves must be integer multiple of 4.

#### 2.10.3 PH Value

Nyquest

User should set PH value in program to meet voice's sample rate or note's frequency. The PH value is derived by formula below:

PH for voice synthesis (in Hex) =  $\frac{SR \times 8 \times CH \times 4096}{F_{INST}} \times Factor$

PH for MIDI synthesis (in Hex) =  $\frac{SR \times 8 \times CH \times 4096}{F_{INST}} \times \frac{F_{NOTE}}{F_{PATCH}} \times Factor$

SR: sample rate of speech waveform or Head/Tail waveform. SR unit is hertz.

CH: the allowable value of CH is listed in table below.

| Active Voice Channel | CH Value                                       |

|----------------------|------------------------------------------------|

| 1                    | 2                                              |

| 2                    | 2                                              |

| 4                    | 4                                              |

| 6                    | 4 for channel 2, 3<br>8 for channel 0, 1, 4, 5 |

| 8                    | 8                                              |

| Active MIDI Channel | CH Value                                       |

|---------------------|------------------------------------------------|

| 2                   | 2                                              |

| 4                   | 4                                              |

| 6                   | 4 for channel 2, 3<br>8 for channel 0, 1, 4, 5 |

| 8                   | 8                                              |

$F_{INST}$ : instruction cycle. It is 4,000,000 or 2,000,000 by mask option.

Factor is 1 if noise filter is disabled, and 2 if noise filter is enabled.

$F_{NOTE}$ : frequency of the note which is being played.

$F_{PATCH}$ : frequency of key note on which patch waveform is based.

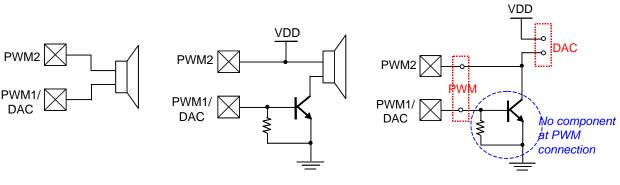

#### 2.10.4 Audio Output

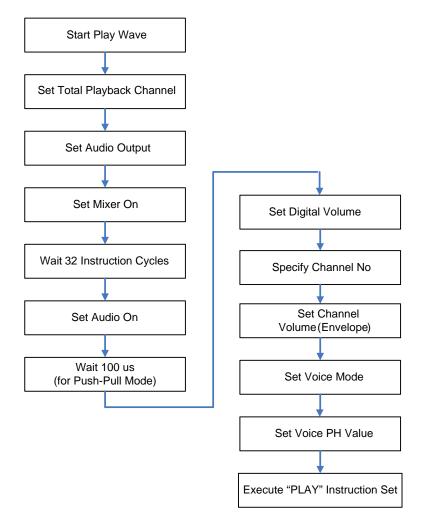

Before using the audio output, user can choose one of the 13-bit Push-Pull (PP), 13-bit DAC or 12-bit PWM as the audio output for NY7. NY7A provides PWM and DAC audio output and NY7B/NY7C provide Push-Pull (PP) and DAC audio output. If user selects Push-Pull, user has to enable the Push-Pull by clearing bit 2 and 3 as zero in CHARC(\$0A) first. It provides hardware ramp-up and ramp-up time is about 100us. Moreover, there are 4 mask options to select Push-Pull gain for volume adjustment. These 4 mask options correspond to 100%, 83%, 66% or 50% of maximum analog volume output. If DAC is selected, ramp-up process has to be implemented by user's application program. If PWM is selected, there is no need of ramp-up.

Besides in NY7A, it provides a pad detecting mechanism to detect whether DAC or PWM is used. The pad detecting mechanism detects the PWM2 pad during the reset initialization period, and sets the initial value of the audio output register as PWM if the PWM2 connection is floating, or sets the initial value of the audio output register as DAC if the PWM2 connection is high. In conclusion, connect the speaker to PWM1 and PWM2 only if using PWM, otherwise connect PWM2 to VDD if using DAC. Since the mechanism sets only the initial value of AUD, don't change the value of the AUD register if the pad detecting mechanism is adopted.

| PWM2 Pad           | Audio Output Initialization |

|--------------------|-----------------------------|

| Speaker (Floating) | PWM                         |

| VDD                | DAC                         |

**PWM Output Connection**

DAC Output Connection

**PWM/DAC Connection Together**

When using the PWM output, we provide an option of normal PWM current or Ultra PWM current for different customer demand. The Ultra PWM current consumes more current but makes sound louder.

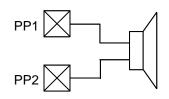

As to connection for Push-Pull output, it just needs to connect PP1 to one terminal of speaker and PP2 to another terminal of speaker.

#### **Push-Pull Output Connection**

#### 2.10.5 Envelope Control

During speech synthesis or melody synthesis, there is one set of 8-bit envelope register (ENVH and ENVL), which can store the envelope information. Therefore NY7 can provide 256-level envelope control for each channel and users can use it as alternative of volume control for each channel. If user wants to have largest volume, value 0xFF is recommended.

As NY7 is a 8-channel synthesizer but there is only one set of envelope register physically, user has to write value to SFR CHNO to select a specific channel and the 256-level envelope data will be updated to this selected channel. Moreover, as NY7 micro-controller is 4-bit but envelope information is 8-bit, the envelope data of selected channel will not be updated until SFR ENVH is written. User can refer Chapter 3.8.6 for details.

#### 2.10.6 Volume Control

NY7 supports 16-step digital volume control by the VOL register. Default value of VOL register is 0x2. In order to have suitable volume, VOL=0x2 is recommended for 8-ch speech/MIDI synthesis. VOL=0x3 is recommended for 6-ch speech/MIDI synthesis. VOL=0x4 is recommended for 4-ch speech/MIDI synthesis. VOL=0x8 is recommended for 2-ch speech/MIDI synthesis. VOL=0xF is recommended for 1-ch speech synthesis.

As sampled waveform of speech or Head/Tail may not fully occupy between maximum and minimum value, user may consider using larger value as digital volume than above recommended value for VOL register in order to have satisfied loudness. Moreover, because there is a Limiter after Mixer to saturate multi-channel synthetic result, it can prevent quality degradation of synthetic result.

# **Chapter 3. System Control**

# 3.1 Introduction of System Function Register

The combination of RPT0~5 are multi-function register pointers. The ENVL/H, CHARC, AUD, CHNO, DECMD, ONOFF and VOL are audio control related registers. INT register is used to control or access the system base timer (BT) and interrupt. The BANK register is used to switch the program bank when targeting branch address is located beyond current program bank. The XMD is RAM indirect access registers. The ROD1 and ROD2 registers are used to read the ROM data. The Px and PxIO are I/O ports registers, here x could A, B, C, D, E or F. As PA, PB, PC, PD, PE and PF are bi-directional I/O ports, SFR PAIO, PBIO, PCIO, PDIO, PEIO and PFIO are used to determine the direction of each I/O pin.

| Addr | Name  | R/W   | Bit        | Data                  | Description                                 | Default  |  |

|------|-------|-------|------------|-----------------------|---------------------------------------------|----------|--|

| \$00 | RPT0  | R/W   | [3:0]      | 0/1                   | Multi-function register pointer [3:0]       | xxxx     |  |

| \$01 | RPT1  | R/W   | [3:0]      | 0/1                   | Multi-function register pointer [7:4]       | xxxx     |  |

| \$02 | RPT2  | R/W   | [3:0]      | 0/1                   | Multi-function register pointer [11:8]      | xxxx     |  |

| \$03 | RPT3  | R/W   | [3:0]      | 0/1                   | 0/1 Multi-function register pointer [15:12] |          |  |

| \$04 | RPT4  | R/W   | [3:0]      | 0/1                   | Multi-function register pointer [19:16]     | xxxx     |  |

| \$05 | RPT5  | R/W   | [0]        | 0/1                   | Multi-function register pointer [20]        | xx       |  |

| \$06 | ENVL  | R/W   | [3:0]      | 0/1                   | Envelope [3:0]                              | xxxx     |  |

| \$07 | ENVH  | R/W   | [3:0]      | 0/1                   | Envelope [7:4]                              | xxxx     |  |

| \$08 | ROD1  | R     | [3:0]      | 0/1                   | ROM Data Latch[7:4]                         | xxxx     |  |

| \$09 | ROD2  | R     | [3:0]      | 0/1                   | ROM Data Latch[11:8]                        | xxxx     |  |

|      |       |       |            | 00                    | 8 channels                                  |          |  |

|      |       |       | [1:0]      | 01                    | 6 channels                                  | 8 CH     |  |

|      |       | [1:0] | 10         | 4 channels            | - °CH                                       |          |  |

| \$0A | CHARC | R/W   |            | 11                    | 2 channels                                  |          |  |

|      |       |       |            | 0x                    | Push-Pull (PP)                              |          |  |

|      |       |       | [3:2]      | 10                    | DAC                                         | PP       |  |

|      |       |       | 11         |                       | PWM                                         |          |  |

| \$0B | AUD   | R     | [3:0]      | 0/1                   | DAC[12:9]                                   | xxxx     |  |

|      |       |       | [0]        | 0/1                   | BT = 0.064 ms                               |          |  |

|      |       | R     | [1]        | 0/1                   | BT = 0.128 ms                               |          |  |

|      |       | N     | [2]        | 0/1                   | BT = 0.256 ms                               |          |  |

| \$0C | INT   |       | [3]        | 0/1                   | BT = 1.024 ms                               |          |  |

| φUC  | 1111  |       | V [1:0] 0' | 00                    | Interrupt ~= 0.064 ms                       |          |  |

|      | 14/   | W     |            | 01                    | Interrupt ~= 0.128 ms                       | 0.064 ms |  |

|      |       |       |            | 10                    | Interrupt ~= 0.256ms                        |          |  |

|      |       |       | 11         |                       | Interrupt ~= 1.024 ms                       |          |  |

| \$0D | DECMD | R/W   | [0]        | 0/1                   | reserved                                    |          |  |

| ΦΟΟ  |       |       | 0/1        | Tail Disable / Enable | Enable                                      |          |  |

# NY7 User Manual

| Addr        | Name            | R/W | Bit       | Data                                      | Description                                   | Default       |

|-------------|-----------------|-----|-----------|-------------------------------------------|-----------------------------------------------|---------------|

|             |                 |     | [2]       | 2] 0/1 Head PCM / ADPCM                   |                                               | ADPCM         |

|             |                 |     | [3]       | 0/1                                       | Tail PCM / ADPCM                              | ADPCM         |

|             |                 |     | [0] 0/1   |                                           | Interrupt Off / On                            | Off           |

| ¢or         |                 |     | [1]       | 0/1                                       | Audio Out Off / On                            | Off           |

| \$0E        | E ONOFF R/W [2] |     | [2]       | 0/1                                       | Noise filter Off / ON @ 16 cycles per channel | OFF           |

|             |                 |     | [3]       | 0/1                                       | Audio Mixer Off / On                          | OFF           |

| \$0F        | VOL             | R/W | [3:0]     | 0/1                                       | Volume level of Mixer                         | 0010          |

| \$10        | BANK            | R/W | [3:0]     | 0/1                                       | Program Bank Register                         | 0000          |

| \$11        | XMD             | R/W | [3:0]     | 0/1                                       | Indexed SRAM data                             | хххх          |

| \$12        | CHNO            | R/W | [3:0]     | 0/1                                       | Active channel select                         | 0000          |

|             |                 | R   | [0.0]     | 0/1                                       | PAIO = 1: Read port A input pad data          | XXXX          |

| \$14        | PA              | ĸ   | [3:0]     | 0/1                                       | PAIO = 0: Read port A output register         | XXXX          |

| <b>φ</b> 14 | PA              | W   | [0.0]     | 0/1                                       | PAIO = 1: wakeup status / pull-high control   | wakeup status |

|             |                 | VV  | [3:0]     | 0/1                                       | PAIO = 0: Write to port A output register     | XXXX          |

| \$15        | PAIO            | R/W | [3:0]     | 0/1                                       | Port A direction = Output / Input             | Input         |

|             |                 | Р   | [2.0]     | 0/1                                       | PBIO = 1: Read port B input pad data          | XXXX          |

| ¢16         | סס              | R   | [3:0]     | 0/1                                       | PBIO = 0: Read port B output register         | хххх          |

| \$16        | PB              | 14/ | [0.0]     | 0/1                                       | PBIO = 1: wakeup status / pull-high control   | wakeup status |

|             |                 | W   | [3:0]     | 0/1                                       | PBIO = 0: Write to port B output register     | xxxx          |

| \$17        | PBIO            | R/W | [3:0]     | 0/1                                       | Port B direction = Output / Input Input       |               |

|             |                 | Б   | [0.0]     | 0/1                                       | PCIO = 1: Read port C input pad data          | хххх          |

| \$18        | PC              | R   | [3:0]     | 0/1                                       | PCIO = 0: Read port C output register         | хххх          |

| φιο         | FC              | W   | [0.0]     | 0/1                                       | PCIO = 1: wakeup status / pull-high control   | wakeup status |

|             |                 | vv  | [3:0]     | 0/1                                       | PCIO = 0: Write to port C output register     | хххх          |

| \$19        | PCIO            | R/W | [3:0]     | 0/1                                       | Port C direction = Output / Input             | Input         |

|             |                 | R   | [3:0] 0/1 |                                           | PDIO = 1: Read port D input pad data          | XXXX          |

| \$1A        | PD              | ĸ   | [3.0]     | 0/1                                       | PDIO = 0: Read port D output register         | хххх          |

| φIA         | FD              | W   | [2:0]     | 0/1                                       | PDIO = 1: wakeup status / pull-high control   | wakeup status |

|             |                 | vv  | [3:0]     | 0/1                                       | PDIO = 0: Write to port D output register     | XXXX          |

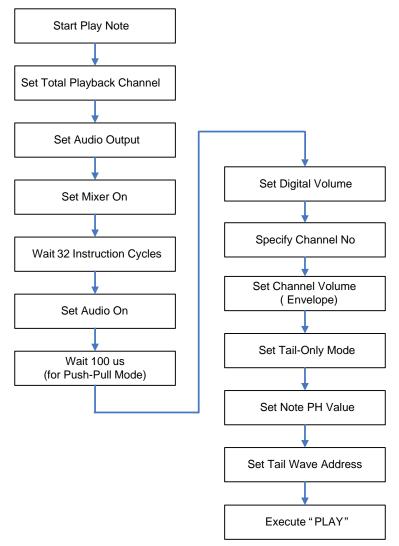

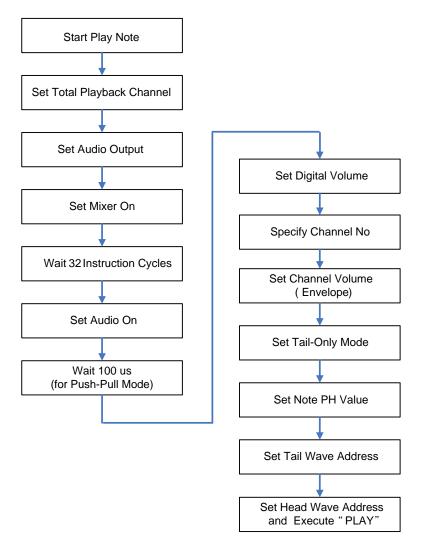

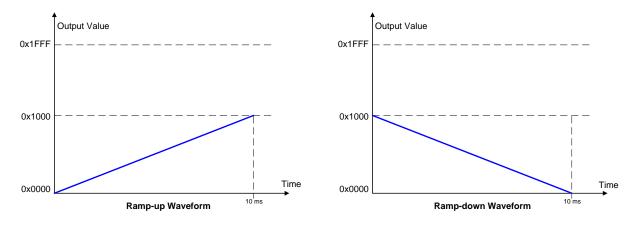

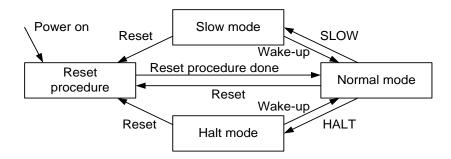

| \$1B        | PDIO            | R/W | [3:0]     | 0/1                                       | Port D direction = Output / Input             | Input         |